Neste tutorial, vamos projetar o CI CD40194 na Plataforma Pitanga. Ao final, você será capaz de experimentar o CD40194 na sua máquina, a uma frequência de clock de 1Hz, explorando todas as funcionalidade deslocamento de bits na C-Board, conforme exemplificado na Figura 1:

Figura 1. Emulando o CI CD40194 na C-Board Virtual Pitanga.

São duas as opções de aprendizado para projetar o CD40194: ou acompanhando o vídeo abaixo com a S-Board, ou seguindo o passo-a-passo descrito neste artigo com a C-Board. Escolha o formato que mais se ajusta ao seu ritmo de aprendizado e vamos começar!

Nota: é recomendado que você já tenha feito os tutoriais Como projetar o CI CD4069 em Verilog e Como projetar o CI CD4081 em Verilog . Estes tutoriais fornecem uma base sólida para entender o processo de desenvolvimento de circuitos digitais na Pitanga.

O que é o Circuito Integrado CD40194?

O circuito integrado CD40194 é um registrador de deslocamento de 4 bits, projetado para armazenar e manipular dados digitais. Ele é capaz de deslocar bits serialmente para a esquerda ou para a direita, dependendo do sinal de controle fornecido 1. Este CI é utilizado em aplicações que requerem armazenamento temporário de dados e manipulação sequencial, como em sistemas de comunicação digital e controle lógico.

O CD40194 faz parte da série CD4000 de circuitos integrados CMOS, comercialmente lançada pela RCA Solid State Division em 19682. Atualmente, este CI é fábricado pela Texas Instruments, e o seu uso em novos designs não é mais recomendado, pois foi substituído por circuitos integrados mais modernos e eficientes. No entanto, o CD40194 ainda é amplamente utilizado em projetos educacionais e hobbyistas, motivo pelo qual iremos utilizá-lo como exemplo neste tutorial.

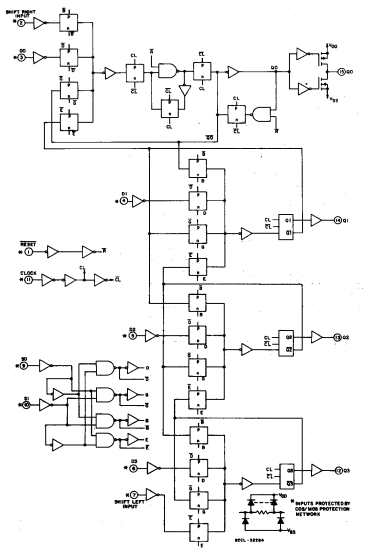

Qual é o diagrama lógico do CD40194?

O diagrama do CI CD40194 pode ser visto na Figura 2. Note que este diagrama é um tanto complexo para ser descrito em Verilog, pois requer descrever diversas conexões e dispositivos de memória. No entanto, Verilog possui formas mais abstratas de descrever circuitos digitais, como veremos mais adiante.

Figura 2. Diagrama lógico do CI CD40194B. Fonte: [1]

Até o momento, você aprendeu a descrever circuitos digitais usando estruturas lógicas com as portas lógicas AND2 e NOT. Chamamos isso de descrição estrutural, ou Verilog estrutural. Neste tipo codificação, descrevemos estruturas e interconexões, como mostrado na Figura 2. Essa abordagem é útil para circuitos simples, com poucos elementos, onde podemos facilmente identificar as portas lógicas e as suas interconexões.

No entanto, o Verilog também permite descrever circuitos digitais de forma mais abstrata, utilizando estruturas comportamentais, como always e assign. Essas estruturas permitem descrever o comportamento do circuito sem se preocupar com a implementação física, tornando o código mais legível e fácil de entender. Essa abordagem é chamada de descrição comportamental, ou Verilog comportamental, e será explorada nas próximas seções deste tutorial.

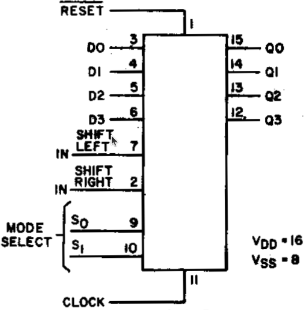

Qual é a pinagem do CI CD40194?

A Figura 3 apresenta o diagrama do bloco topo do CI CD40194. Nele, é possível identificar os pinos de entrada e saída. Normalmente, diagramas como este posicionam os pinos de entrada à esquerda - com os pinos D0 a D3 - e os pinos de saída à direita - como os pinos Q0 à Q3. Pinos de sistema, por vezes, são posicionados acima ou abaixo do bloco, tal como os pinos RESET e CLOCK. No entanto, para um iniciante na área, essa informação não é conhecida, sendo necessário um descritivo dos pinos. Esse descritivo pode ser encontrado no datasheet do componente eletrônico em forma de texto, em forma de tabela, ou em ambos os formatos.

Figura 3. Diagrama do bloco topo do CI CD40194B. Adaptado de [1]

A Tabela 1 apresenta a descrição dos pinos do CI CD40194B. Com base no diagrama do bloco topo da Figura 3 e as informações no datashet do CD40194B, construímos a Tabela 1. Para cada pino do CD40194 essa tabela apresenta a seguinte informação: numeração do pino, direção de sinal (entrada ou saída), condição de ativação para sinais de controle, e uma breve descrição funcional.

| Nome do Pino | Número do Pino | Direção | Ativo | Descrição |

|---|---|---|---|---|

| D0, D1, D2, D3 | 03, 04, 05, 06 | Entrada | - | Entrada paralela de dados para o registrador de deslocamento de 4 bits |

| Q0, Q1, Q2, Q3 | 15, 14, 13, 12 | Saída | - | Saída paralela de dados do registrador de deslocamento de 4 bits |

| SHIFT LEFT | 07 | Entrada | - | Entrada serial de dados para o registrador de deslocamento (esquerda) |

| SHIFT RIGHT | 02 | Entrada | - | Entrada serial de dados para o registrador de deslocamento (direita, Q0) |

| S0 | 09 | Entrada | 1 | Em conjunto com S1, define o modo de operação do CD40194 (ver figura 3) |

| S1 | 10 | Entrada | 1 | Em conjunto com S0, define o modo de operação do CD40194 (ver figura 3) |

| CLOCK | 11 | Entrada | / | Relógio do sistema. Dados são capturados a cada borda de subida |

| RESET | 01 | Entrada | 0 | Inicializa o CI CD40194 quando ativo em 0 |

| Vdd | 16 | Entrada | 1 | Fonte de alimentação positiva |

| Vss | 08 | Entrada | 1 | Fonte de alimentação negativa |

Tabela 1. Descrição dos pinos do CI CD40194B. Adaptado de [1].

Descrevendo o comportamento do CI CD40194?

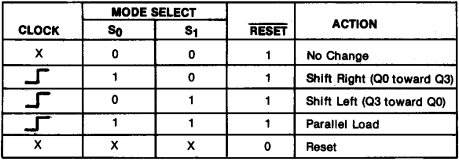

O comportamento do CD40194 é resumidamente descrito através da tabela verdade na Figura 4. Nela, cada linha corresponde a uma combinação dos sinais de entrada CLOCK, S0, S1 e RESET. Para cada combinação de entradas, há um comportamento específico do CI CD40194, conforme indicado na coluna ACTION da tabela a seguir:

Figura 4. Tabela verdade do CI CD40194B. Adaptado de [1].

O projeto do CD40194 será implementado em duas etapas. Primeiramente, descreveremos a interface do módulo cd40194 com o auxílio da Tabela 1. Em seguida, implementaremos a arquitetura - ou o comportamento - do módulo cd40194 com o auxílio da Tabela Verdade indicada na Figura 4. Vamos começar pela descrição da interface do módulo cd40194 em Verilog, declarando os sinais de entrada e saída da Tabela 1:

module cd40194(CLOCK, RESET, SHIFT_LEFT, SHIFT_RIGHT, S, D, Q);

input CLOCK;

input RESET;

input [1:0] S;

input SHIFT_LEFT;

input SHIFT_RIGHT;

input [3:0] D;

output reg [3:0] Q;

// continua ...

Observe que sinais compostos por múltiplos bits são declarados utilizando intervalos numéricos entre colchetes, representando a largura do barramento. Este é o caso do sinal S e do sinal D e Q. O número mais a esquerda do intervalo indica o bit mais significativo (MSB) e o número mais à direita indica o bit menos significativo (LSB). Por exemplo, S[1:0] indica que o sinal S é composto por 2 bits, onde S[1] é o bit mais significativo e S[0] é o bit menos significativo. Da mesma forma, D[3:0] e Q[3:0] indicam que os sinais D e Q são compostos por 4 bits, sendo D[3] e Q[3] os bits mais significativos e D[0] e Q[0] os bits menos significativos.

Além disso, perceba que o sinal Q é declarado como output reg, indicando que este sinal é um elemento de memória. Em Verilog, o tipo reg é utilizado para declarar sinais que podem armazenar valores e ser atualizados. Neste projeto, o sinal Q será utilizado para armazenar o estado do registrador de deslocamento de 4 bits do CD40194, como veremos a seguir na descrição da arquitetura do módulo cd40194:

// behavioral description (architecture)

always@(posedge CLOCK) begin

if(RESET)

Q <= 4'b0000;

else if(S == 2'b11)

// parallel load mode

Q <= D;

else if (S == 2'b10) begin

// shift left mode

Q[3] <= SHIFT_LEFT;

Q[2] <= Q[3];

Q[1] <= Q[2];

Q[0] <= Q[1];

end

else if (S == 2'b01) begin

// shift right mode

Q[0] <= SHIFT_RIGHT;

Q[1] <= Q[0];

Q[2] <= Q[1];

Q[3] <= Q[2];

end

else

Q <= Q;

end

endmodule

No trecho de código acima, temos a construção always@(posedge CLOCK), que indica que o bloco de código dentro dela será executado a cada borda de subida do sinal CLOCK. Dentro deste bloco, temos uma estrutura condicional if que verifica o estado do sinal RESET. Se RESET estiver ativo, o registrador Q é zerado. Caso contrário, o comportamento do CD40194 é determinado pelo valor do sinal S, conforme descrito na Tabela Verdade da Figura 4.

Importante salientar que, na descrição original do CD40194, o sinal RESET é ativo em nível lógico baixo (0). No entanto, na implementação acima, o sinal RESET é tratado como ativo em nível lógico alto (1). Essa alteração é necessária para que o projeto seja compatível com os botões virtuais da C-Board (btn0, btn1 e btn2), que são ativos em nível lógico alto (1).

Mapeando o CI CD40194 para a C-Board

Para mapear o CI CD40194 para o componentes virtuais da C-Board, precisamos codificar o arquivo de pinagem pinout.pitanga. O código abaixo apresenta este mapeamento, utilizando um relógio de 1Hz:

//MODULE PORT BOARD COMPONENT

CLOCK = clk_1hz;

RESET = btn0;

SHIFT_RIGHT = btn1;

SHIFT_LEFT = btn2;

// mode selection

S[0] = sw0;

S[1] = sw5;

// parallel data

D[0] = sw1;

D[1] = sw2;

D[2] = sw3;

D[3] = sw4;

// shift register output

Q[0] = led4;

Q[1] = led3;

Q[2] = led2;

Q[3] = led1;

A próxima etapa é verificar se o código está corente, compilando-o na Pitanga. Para isso, acesse a sua conta Pitanga e, usando a Placa Virtual C (C-Board), copie e cole o código Verilog e o de pinagem acima nos editores Verilog e de Pinos, respectivamente. Clique no botão “Run”. O resultado será mostrado no terminal de saída da Pitanga e deve ser igual ao mostrado abaixo:

Top level design units:

cd40194

Build succeeded: 0 errors, 0 warnings

DESIGN SUMMARY REPORT

module : cd40194

design file: pitanga.v

pinout file: pitanga.pinout

Total number of wires: 42

Total number of cells: 32

Total number of ports: 16

Cell Instances Cell Instances Cell Instances

-----------------------------------------------------------------

AND2 1 | NAND2 8 | XOR2 0

AND3 0 | NAND3 8 | XOR3 0

AND4 4 | NAND4 0 | XOR4 0

OR2 0 | NOR2 5 | XNOR2 0

OR3 0 | NOR3 0 | XNOR3 0

OR4 0 | NOR4 0 | XNOR4 0

-----------------------------------------------------------------

BUF 0 | INV 2 | DFFRSE 4

Cells utilization: 32

Transistor count : 302/500 transistors (60.40 %)

A tabela acima mostra que o projeto do CD40194 utiliza 32 células lógicas, sendo 1 porta AND2, 8 portas NAND2, 4 portas AND4, 8 portas NAND3, 5 portas NOR2 e 2 inversores. O número total de transistores utilizados é de 302, o que corresponde a aproximadamente 60% da capacidade total da C-Board. Isso indica que o projeto está bem dimensionado para os limites da placa.

Emulando o CI CD40194 na C-Board

De acordo com o arquivo de pinagem, as chaves sw1 a sw4 são utilizadas para carregar os dados de entrada do registrador de deslocamento, enquanto as chaves sw0 e sw5 são utilizadas para selecionar o modo de operação do CD40194. Quando:

- a chave

sw0está ativada, o registrador opera no modo de deslocamento de bits para a direita - a chave

sw5está ativada, o registrador opera no modo de deslocamento de bits para a esquerda - as cahves

sw0esw5estão ativadas, o registrador opera no modo de carregamento paralelo, capturando os bits nas chavessw1asw4

Sabendo disso, podemos criar casos de testes para verificar o fucionamento do CD40194. Os passos a seguir apresentam um exemplo de teste:

- configure um vetor de 4 bits em ‘1’ lógico, ativando as chaves de

sw1asw4 - carregue este vetor de bits no registrador de deslocamento, ativando as chaves

sw0esw5(parallel load mode) - selecione o modo de deslocamento de bits para a direita, desativando a chave

sw5e mantendo a chavesw0ativada - perceba os 4 bits sendo deslocados para a direita em 4 bordas de subida de

CLOCK(shift right mode); - configure, novamente, um vetor de 4 bits em ‘1’ lógico, ativando as chaves de

sw1asw4 - carregue este vetor de bits no registrador de deslocamento, ativando as chaves

sw0esw5(parallel load mode) - selecione o modo de deslocamento de bits para a esquerda, desativando a chave

sw0e mantendo a chavesw5ativada - perceba os 4 bits sendo deslocados para a esquerda em 4 bordas de subida de

CLOCK(shift left mode);

Caso tenha dúvidas, veja a animação da Figura 5 e siga a sequência de passos para verificar se o seu projeto está funcionando.

Figura 5. Exemplo de emulação do CI CD40194 na C-Board Virtual Pitanga.

Visualizando o relógio do sistema no CD40194

Uma situação muito comum que ocorre quanto estamos emulando circuitos digitais síncronos é a dificuldade de visualizar o relógio do sistema. Para resolver essa limitação, uma técnica muito comum que podemos utilizar é conectar o sinal de relógio do sistema - CLOCK - a um LED. Dessa forma, podemos visualizar o sinal de relógio em tempo real, facilitando a depuração e o entendimento do comportamento do circuito. A Figura 6 apresenta um exemplo de como fazer isso, utilizando o led a do display de sete segmentos 0.

Figura 6. Visualizando o sinal de relógio do sistema no CD40194.

Para implementar essa melhoria no CD40194, precisamos

- adicionar uma nova porta saída no módulo

cd40194, chamada deledclk - implementar uma nova conexão entre o sinal de entrada

CLOCKe a portaledclk - mapear a porta

ledclkpara um LED qualquer da C-Board, como, por exemplo, o segmentoado display de sete segmentos0(segd0.a_on)

A seguir, segue o código Verilog, com modificações 1 e 2. Perceba que a alteração 2 é realizada através da atribuição assign ledclk = CLOCK;. A construção assign deve ser utilizada sempre que você precisar conectar um sinal de entrada a uma porta de saída, ou quando você precisar conectar sinais internos.

module cd40194(CLOCK, RESET, SHIFT_LEFT, SHIFT_RIGHT, S, D, Q, ledclk);

input CLOCK;

input RESET;

input SHIFT_LEFT;

input SHIFT_RIGHT;

input [1:0] S;

input [3:0] D;

output ledclk; //new output for clock visualization

output reg [3:0] Q;

assign ledclk = CLOCK; // connect CLOCK to ledclk

// behavioral description (architecture)

always@(posedge CLOCK) begin

if(RESET)

Q <= 4'b0000;

else if(S == 2'b11)

// parallel load mode

Q <= D;

else if (S == 2'b10) begin

// shift left mode

Q[3] <= SHIFT_LEFT;

Q[2] <= Q[3];

Q[1] <= Q[2];

Q[0] <= Q[1];

end

else if (S == 2'b01) begin

// shift right mode

Q[0] <= SHIFT_RIGHT;

Q[1] <= Q[0];

Q[2] <= Q[1];

Q[3] <= Q[2];

end

else

Q <= Q;

end

endmodule

Para o mapeamento do sinal ledclk para o segmento a do display de sete segmentos 0, basta adicionar a seguinte linha ao arquivo de pinagem pinout.pitanga:

//MODULE PORT BOARD COMPONENT

CLOCK = clk_1hz;

RESET = btn0;

SHIFT_RIGHT = btn1;

SHIFT_LEFT = btn2;

ledclk = segd0.a_on; // connect ledclk to segment 'a' of display '0'

// mode selection

S[0] = sw0;

S[1] = sw5;

// parallel data

D[0] = sw1;

D[1] = sw2;

D[2] = sw3;

D[3] = sw4;

// shift register output

Q[0] = led4;

Q[1] = led3;

Q[2] = led2;

Q[3] = led1;

Pronto! Agora, ao emular o CD40194 na C-Board, você poderá visualizar o sinal de relógio do sistema no LED a do display de sete segmentos 0. Isso facilitará a depuração e o entendimento do comportamento do circuito. Experimente outros comportamentos do CD40194, tal como injetar novos bits no registrador de deslocamento através da porta SHIFT_RIGHT (botão btn1) ou SHIFT_LEFT (botão btn2). Reinicialize o circuito pressionando o botão RESET (botão btn0). Perceba que os leds led1 a led4 acendem somente nas bordas de subida do sinal de relógio.

Conclusão

Parabéns por concluir este tutorial! Agora você já sabe como implementar o circuito integrado CD40194 em Verilog, mapear seus sinais para os componentes virtuais da C-Board e compilar o projeto com sucesso. Utilizando a Placa Virtual Pitanga, você pôde experimentar na prática o desenvolvimento de circuitos digitais com Verilog. Este conhecimento pode ser aplicado também em FPGAs ou diretamente em semicondutores, assuntos que serão explorados em futuros tutoriais.

Referências

Texas Instruments. “CD40194B – Datasheet (Shift Register CMOS Bidirecional de 4 Bits).” [Online]. Disponível em: https://www.ti.com/lit/ds/symlink/cd40194b.pdf . Acesso em: 22-Jul-2025. ↩︎

Radio Corporation of America. “CMS-272 RCA COSMOS Manual.” Internet Archive, 1979. [Online]. Disponível em: https://archive.org/details/cms-272-rca-cosmos-manual/page/2/mode/2up . Acesso em: 22-Jul-2025. ↩︎