Projetar o circuito integrado (CI) CD4069 em Verilog é extremamente simples, sendo uma ótima alternativa para aqueles que desejam aprender a projetar circuitos digitais semicondutores sem FPGA e tendo como base componentes eletrônicos conhecidos do mercado. Neste tutorial, iremos demonstrar como projetar este circuito na Plataforma Pitanga. Ao final, você será capaz de experimentar o CD4069 na sua máquina, em tempo real e sem FPGA, emulando-o na C-Board, conforme indicado na Figura 1:

Figura 1. Emulando o circuito integrado CD4069 na C-Board Virtual Pitanga.

Dois são os caminhos que o levarão até o resultado final deste tutorial. O primeiro é através do vídeo-tutorial abaixo. O segundo é através deste artigo, onde você encontrará uma descrição detalhada de cada etapa do projeto. Escolha o caminho que mais lhe agrada e vamos começar!

O que é o Circuito Integrado CD4069?

O circuito integrado CD4069 foi introduzido no mercado em meados de 1968 pela empresa americana RCA1 (Radio Corporation of America). Esta empresa introduziu a série de circuitos integrados digitais CMOS 40002, ainda disponível no mercado nos dias atuais pela Texas Instruments3.

Originalmente, esta série de circuitos integrados foi lançada com nodo tecnológico de 20 μm, o que significa que os transistores eram fabricados com uma largura de canal de 20 micrômetros. Com o passar do tempo, a tecnologia evoluiu e as larguras de canal foram reduzidas, permitindo a fabricação de circuitos integrados mais compactos e eficientes.

Qual é a pinagem e o diagrama lógico do CD4069?

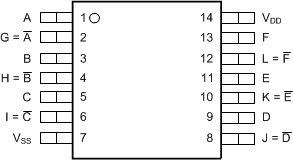

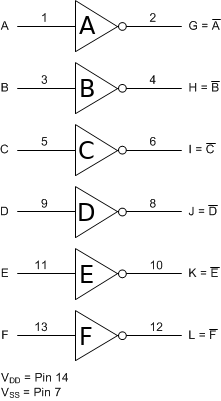

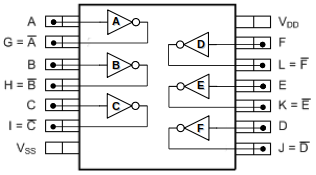

O CD4069 é composto por 6 portas lógicas inversoras independentes. No seu datasheet4 podem ser encontrados o diagrama de porta lógicas, a disposição dos pinos no encapsulamento do CD4069, bem como a descrição detalhada da funcionalidade de cada pino. As Figuras 2 e 3, a seguir mostram, respectivamente, a disposição dos pinos no encapsulamento e o diagrama lógico do circuito integrado CD4069UB da Texas Instruments.

Figura 2. Configuração de pinos do CI CD4069UB. Fonte: [4]

Figura 3. Esquemático lógico do CI CD4069UB. Adaptado de [4]

Nas seções seguintes, será desenvolvido o circuito integrado CD4069 utilizando a Plataforma Pitanga. A partir das Figuras 2 e 3, será descrito o circuito em Verilog, bem como o mapeamento das entradas e saídas para os componentes da Placa Virtual Pitanga C-Board. Na sequência, o projeto será compilado e submetido à análise com base nos relatórios de design gerados pela ferramenta. Por fim, será realizada a emulação do circuito na C-Board, permitindo a interação prática e a verificação do seu funcionamento em conformidade com as especificações descritas no datasheet da fabricante Texas Instruments.

Descrevendo a Interface do CD4069

As figuras 2 e 3 apresentam a configuração dos pinos do CD4069 e o seu correspondente diagrama lógico. A partir dessas informações, é possível construir a tabela 1, indicando quais pinos são de entrada e quais pinos são de saída, bem como a descrição de cada pino.

| Pino | Direção | Descrição |

|---|---|---|

| A | Entrada | Pino de entrada para o Inversor A |

| B | Entrada | Pino de entrada para o Inversor B |

| C | Entrada | Pino de entrada para o Inversor C |

| D | Entrada | Pino de entrada para o Inversor D |

| E | Entrada | Pino de entrada para o Inversor E |

| F | Entrada | Pino de entrada para o Inversor F |

| G | Saída | Pino de saída do Inversor A |

| H | Saída | Pino de saída do Inversor B |

| I | Saída | Pino de saída do Inversor C |

| J | Saída | Pino de saída do Inversor D |

| K | Saída | Pino de saída do Inversor E |

| L | Saída | Pino de saída do Inversor F |

| Vdd | - | Fonte de alimentação positiva |

| Vss | - | Fonte de alimentação negativa |

Tabela 1. Descrição dos pinos do CI CD4069UB. Adaptado de [4].

A partir dessa tabela, podemos descrever, ou modelar, a interface de comunicação do CI CD4069 em Verilog, conforme o código a seguir:

module cd4069(

input A, B, C, D, E, F,

output G, H, I, J, K, L

);

endmodule

Feito a modelagem inicial, vamos verificar se o código está corente compilando-o na Pitanga. Para isso, acesse a sua conta Pitanga e, usando a Placa Virtual C (C-Board), copie e cole o código acima no Editor Verilog. O Editor Verilog está indicado na Figura 4 a seguir, assim como o Editor de Pinos e o Terminal de Saída da Pitanga.

Figura 4. Descrição da interface do CI CD4069UB na Pitanga

Em seguida, apague o código padrão localizado no Editor de Pinos (se houver) e compile o projeto clicando no botão “Run” localizado no lado direto da C-Board. Também é possível compilar o projeto clicando no ícone “Run” localizado no canto esquerdo inferior da barra lateral de ícones (veja a Figura 4). Fazendo isso, o seguinte relatório deve ser impresso no terminal de saída da Pitanga:

Top level design units:

CD4069

Build succeeded: 0 errors, 0 warnings

Error: mismatched input '<EOF>' expecting {COMPONENT_ID, Identifier} in line 1:1 on file: pitanga.pinout

Embora o código tenha sido compilado com sucesso, a ferramenta reportou um erro no arquivo pitanga.pinout. Esse erro ocorre porque este arquivo — localizado no Editor de Pinos e responsável por mapear as conexões lógicas internas do circuito projetado aos pinos de saída — encontra-se vazio. Em outras palavras, o módulo Verilog foi devidamente compilado, porém não há qualquer vínculo entre os componentes virtuais da C-Board e a funcionalidade interna do circuito descrito em Verilog.

Para resolver esse problema, é necessário desenvolver a lógica interna do CD4069 e realizar o mapeamento adequado para os componentes virtuais da C-Board. Esse será exatamente o foco da próxima seção.

Descrevendo a Funcionalidade do CD4069 com um Inversor

O circuito integrado CD4069 é constituído por seis portas lógicas inversoras independentes. No entanto, antes de prosseguir com o desenvolvimento do projeto completo, será abordada inicialmente a funcionalidade de apenas uma dessas portas inversoras, conforme demonstrado a seguir.

module cd4069(

input A, B, C, D, E, F,

output G, H, I, J, K, L

);

// Descrição de uma porta lógica inversora

not(G, A);

endmodule

Na implementação acima, a porta lógica inversora foi descrita utilizando a construção not. Em Verilog, essa construção recebe dois parâmetros: o primeiro corresponde à saída da porta lógica e o segundo à entrada. Como o módulo CD4069 já possui os sinais G (saída) e A (entrada) previamente declarados como portas, não é necessário criar sinais intermediários para conectá-los à instância da porta not. O compilador reconhece automaticamente que os nomes referem-se aos mesmos sinais definidos na interface do módulo.

Nota: Neste tutorial, o termo “porta” é utilizado em dois contextos distintos: para representar elementos funcionais — como as portas lógicas — e para indicar as interfaces de entrada e saída de um módulo em Verilog. Essa sobreposição de significados pode gerar confusão, sobretudo para quem está começando. Por essa razão, sempre que possível, adotaremos a expressão “porta lógica” para nos referirmos a componentes funcionais (como inversores ou AND), e reservaremos o termo “porta” exclusivamente para tratar das interfaces de conexão de módulos Verilog.

Agora, precisamos mapear as portas G e A do módulo CD4069 para os componentes virtuais da C-Board. Neste tutorial, iremos mapear a porta G para o LED led0 e a porta A para a chave deslizante sw0. O código de pinagem, portanto, será o seguinte:

// Texto seguido de duas barras consectivas não é processado pela Pitanga

// PORTA COMPONENTE NA PLACA

A = sw0;

G = led0;

Copie e cole o código Verilog e o de Pinagem acima nos editores Verilog e de Pinos, respectivamente. Em seguida, compile o código clicando no botão “Run”. O resultado será mostrado no terminal de saída da Pitanga, conforme indicado abaixo:

Top level design units:

CD4069

Build succeeded: 0 errors, 0 warnings

ERROR: Found 5 problems in 'check -assert'.

Warning: Wire CD4069.\H is used but has no driver.

Warning: Wire CD4069.\I is used but has no driver.

Warning: Wire CD4069.\J is used but has no driver.

Warning: Wire CD4069.\K is used but has no driver.

Warning: Wire CD4069.\L is used but has no driver.

Perceba que os 5 erros de projeto estão relacionados com as portas H, I, J, K e L. Estas portas, localizadas no módulo CD4069, não possuem funcionalidade alguma no projeto. Para corrigir este problema, iremos remover essas portas do módulo CD4069, juntamente com as portas de entrada B, C, D, E e F. Dessa forma, manteremos apenas as portas necessárias para a descrição de uma única porta lógica inversora. O código corrigido encontra-se a seguir:

module cd4069(

input A,

output G

);

// Descrição de uma porta lógica inversora

not(G, A);

endmodule

Emulando o CD4069 com apenas um Inversor

Copie e cole código da seção anterior no editor Verilog. Compile novamente o projeto, clicando no botão “Run”. O resultado da compilação do projeto será impresso no terminal da Pitanga.

Top level design units:

CD4069

Build succeeded: 0 errors, 0 warnings

DESIGN SUMMARY REPORT

module : CD4069

design file: pitanga.v

pinout file: pitanga.pinout

Total number of wires: 2

Total number of cells: 1

Total number of ports: 4

Cell Instances Cell Instances Cell Instances

-----------------------------------------------------------------

AND2 0 | NAND2 0 | XOR2 0

AND3 0 | NAND3 0 | XOR3 0

AND4 0 | NAND4 0 | XOR4 0

OR2 0 | NOR2 0 | XNOR2 0

OR3 0 | NOR3 0 | XNOR3 0

OR4 0 | NOR4 0 | XNOR4 0

-----------------------------------------------------------------

BUF 0 | INV 1 | DFFRSE 0

Cells utilization: 1

Transistor count : 2/500 transistors (0.40 %)

Note que a Pitanga não reporta mais erros e indica o uso de uma porta lógica inversora (INV) no relatório de design. Este comportamento pode ser visto na C-Board indicada na Figura 5 através do LED led0 ligado enquanto a chave deslizante sw0 está desativada. Quando a chave sw0 é ativada, o LED led0 se apaga, indicando que o circuito está invertendo o sinal lógico da chave deslizante sw0.

Figura 5. Emulação de uma porta lógica inversora.

No relatório de design, é possível observar a presença de 2 wires (fios) e 4 ports (portas). Os dois fios correspondem às conexões entre a porta lógica interna INV e os sinais de entrada A e G. As quatro portas, por sua vez, referem-se aos pinos A, G, Vdd e Vss, conforme ilustrado na Figura 2. Embora os pinos de alimentação Vdd e Vss não sejam explicitamente declarados no módulo Verilog, a Plataforma Pitanga os reconhece e os contabiliza automaticamente no relatório de design, garantindo conformidade com a estrutura física do CI.

Descrevendo a Funcionalidade completa do CD4069

No momento que conseguimos emular uma única porta inversora do CD4069, podemos facilmente emular o CD4069 em sua totalidade. É isso que vamos fazer a seguir. A partir das Figuras 2 e 3, vamos elaborar uma figura adicional e mais completa. Esta figura, unindo a configuração dos pinos e o esquemático lógico do CD4069, é mostrada na Figura 6.

Figura 6. Esquemático lógico-funcional do CI CD4069UB.

A partir da Figura 6, vamos descrever a funcionalidade do CD4069 em Verilog. Para isso, devemos replicar a mesma construção de porta inversora 5 vezes, alterando os parâmetros das portas de entrada e saída dos inversores. Veja a Figura 6 e descreva o restante do circuito. Caso precise de ajuda, o código completo está a logo abaixo.

module cd4069(

input A, B, C, D, E, F,

output G, H, I, J, K, L

);

// Descrição lógica do CD4069 (6 inversores independentes)

not(G, A);

not(H, B);

not(I, C);

not(J, D);

not(K, E);

not(L, F);

endmodule

Lembre-se que também é necessário mapear as portas de entrada e saída do módulo CD4069 para os componentes da C-Board. O código de pinagem, portanto, será o seguinte:

// Sintaxe:

// <port> = <serigrafia do componente na placa>

// portas de entrada do CD4069

A = sw0;

B = sw1;

C = sw2;

D = sw3;

E = sw4;

F = sw5;

// portas de saída do CD4069

G = led0;

H = led1;

I = led2;

J = led3;

K = led4;

L = led5;

Por fim, copie e cole o código Verilog e o de Pinagem acima nos editores Verilog e de Pinos, respectivamente. Em seguida, compile o código clicando no botão “Run”. O resultado da compilação do projeto será impresso no terminal da Pitanga, conforme indicado abaixo:

Top level design units:

CD4069

Build succeeded: 0 errors, 0 warnings

DESIGN SUMMARY REPORT

module : CD4069

design file: pitanga.v

pinout file: pitanga.pinout

Total number of wires: 12

Total number of cells: 6

Total number of ports: 14

Cell Instances Cell Instances Cell Instances

-----------------------------------------------------------------

AND2 0 | NAND2 0 | XOR2 0

AND3 0 | NAND3 0 | XOR3 0

AND4 0 | NAND4 0 | XOR4 0

OR2 0 | NOR2 0 | XNOR2 0

OR3 0 | NOR3 0 | XNOR3 0

OR4 0 | NOR4 0 | XNOR4 0

-----------------------------------------------------------------

BUF 0 | INV 6 | DFFRSE 0

Cells utilization: 6

Transistor count : 12/500 transistors (2.40 %)

Note que o relatório de design indica o uso de 6 portas lógicas inversoras (INV), o equivalente a 12 transistores CMOS5. Este é exatamente o resultado esperado de consumo de lógica para um CD4069, pois cada porta lógica inversora utiliza 2 transistores CMOS.

Emulando o Circuito Integrado CD4069 na Pitanga C-Board

Agora é o momento ideal para explorar e interagir com seu projeto, observando o comportamento dinâmico do circuito na C-Board.

Para isso, ative e desative as chaves deslizantes sw0 a sw5, observando o comportamento dos LEDs led0 a led5. Cada LED deve acender quando a chave correspondente estiver desativada (0) e apagar quando a chave estiver ativada (1). Este comportamento é exatamente o que se espera de um circuito integrado CD4069, que consiste em 6 portas lógicas inversoras independentes, representado na animação da Figura 1, apresentada no início deste tutorial, e novamente ilustrado na Figura 7 a seguir.

Figura 7. Exemplo de emulação do CI CD4069 na C-Board Virtual Pitanga.

Conclusão

Se você chegou até aqui, parabéns! Isso significa que conseguiu projetar o circuito integrado CD4069 em Verilog, realizar o mapeamento dos sinais para os componentes virtuais da C-Board e compilar o projeto sem erros. Com o auxílio da Placa Virtual Pitanga, você obteve a experiência de projetar em Verilog, podendo implementar este mesmo projeto em dispositivos lógico-programáveis (FPGAs) ou em semicondutores, assuntos que iremos explorar em outros tutoriais.

Referências

Wikipedia. “Radio Corporation of America.” [Online]. Disponível em: https://en.wikipedia.org/wiki/RCA . Acesso em: 21-Jul-2025. ↩︎

B. Lojek, History of Semiconductor Engineering. Berlin, Germany: Springer, 2007. ↩︎

Texas Instruments. “Site oficial.” [Online]. Disponível em: https://www.ti.com/ . Acesso em: 21-Jul-2025. ↩︎

[8] Texas Instruments. “CD4069UB – Datasheet.” [Online]. Disponível em: https://www.ti.com/document-viewer/CD4069UB/datasheet . Acesso em: 21-Jul-2025. ↩︎

N. H. E. Weste e D. M. Harris, CMOS VLSI Design: A Circuits and Systems Perspective, 4ª ed. Boston, MA, EUA: Addison-Wesley, 2011. ↩︎